# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Alfred Kobsa University of California, Irvine, CA, USA Friedemann Mattern ETH Zurich, Zürich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Gerhard Weikum Max Planck Institute for Informatics, Saarbruecken, Germany

For further volumes: http://www.springer.com/series/7407

Roman Wyrzykowski · Jack Dongarra Konrad Karczewski · Jerzy Waśniewski (Eds.)

# Parallel Processing and Applied Mathematics

10th International Conference, PPAM 2013 Warsaw, Poland, September 8–11, 2013 Revised Selected Papers, Part I

*Editors* Roman Wyrzykowski Konrad Karczewski Institute of Computer and Information Science Czestochowa University of Technology Czestochowa Poland

Jack Dongarra Department of Computer Science University of Tennessee Knoxville, TN USA Jerzy Waśniewski Informatics and Mathematical Modelling Technical University of Denmark Kongens Lyngby Denmark

ISSN 0302-9743 ISSN 1611-3349 (electronic) ISBN 978-3-642-55223-6 ISBN 978-3-642-55224-3 (eBook) DOI 10.1007/978-3-642-55224-3 Springer Heidelberg New York Dordrecht London

Library of Congress Control Number: 2014937670

LNCS Sublibrary: SL1 - Theoretical Computer Science and General Issues

#### © Springer-Verlag Berlin Heidelberg 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Preface

This volume comprises the proceedings of the 10th International Conference on Parallel Processing and Applied Mathematics, PPAM 2013, which was held in Warsaw, Poland, September 8–11, 2013. The jubilee PPAM conference was organized by the Department of Computer and Information Science of the Czestochowa University of Technology, under the patronage of the Committee of Informatics of the Polish Academy of Sciences, in cooperation with the Polish-Japanese Institute of Information Technology. The main organizer was Roman Wyrzykowski.

PPAM is a biennial conference. Nine previous events have been held in different places in Poland since 1994. The proceedings of the last six conferences have been published by Springer-Verlag in the *Lecture Notes in Computer Science* series (Nałęczów, 2001, vol. 2328; Częstochowa, 2003, vol. 3019; Poznań, 2005, vol. 3911; Gdańsk, 2007, vol. 4967; Wrocław, 2009, vols. 6067 and 6068; Toruń, 2011, vols. 7203 and 7204).

The PPAM conferences have become an international forum for exchanging ideas between researchers involved in parallel and distributed computing, including theory and applications, as well as applied and computational mathematics. The focus of PPAM 2013 was on models, algorithms, and software tools that facilitate efficient and convenient utilization of modern parallel and distributed computing architectures, as well as on large-scale applications.

This meeting gathered the largest number of participants in the history of PPAM conferences – more than 230 participants from 32 countries. A strict refereeing process resulted in the acceptance of 143 contributed presentations, while approximately 44 % of the submissions were rejected. Regular tracks of the conference covered such important fields of parallel/distributed/cloud computing and applied mathematics as:

- Numerical algorithms and parallel scientific computing

- Parallel non-numerical algorithms

- Tools and environments for parallel/distributed/cloud computing

- Applications of parallel computing

- Applied mathematics, evolutionary computing, and metaheuristics

The plenary and invited talks were presented by:

- Fran Berman from the Rensselaer Polytechnic Institute (USA)

- Ewa Deelman from the University of Southern California (USA)

- Jack Dongarra from the University of Tennessee and Oak Ridge National Laboratory (USA), and University of Manchester (UK)

- Geoffrey Ch. Fox from Indiana University (USA)

- Laura Grigori from Inria (France)

- Fred Gustavson from the IBM T.J. Watson Research Center (USA)

- Georg Hager from the University of Erlangen-Nuremberg (Germany)

- Alexey Lastovetsky from the University College Dublin (Ireland)

#### VI Preface

- Miron Livny from the University of Wisconsin (USA)

- Piotr Luszczek from the University of Tennessee (USA)

- Rizos Sakellariou from the University of Manchester (UK)

- James Sexton from the IBM T.J. Watson Research Center (USA)

- Leonel Sousa from the Technical University of Lisbon (Portugal)

- Denis Trystram from the Grenoble Institute of Technology (France)

- Jeffrey Vetter from the Oak Ridge National Laboratory and Georgia Institute of Technology (USA)

- Richard W. Vuduc from the Georgia Institute of Technology (USA)

- Robert Wisniewski from Intel (USA)

Important and integral parts of the PPAM 2013 conference were the workshops:

- Minisympsium on GPU Computing organized by José R. Herrero from the Universitat Politecnica de Catalunya (Spain), Enrique S. Quintana-Ortí from the Universidad Jaime I (Spain), and Robert Strzodka from NVIDIA

- Special Session on Multicore Systems organized by Ozcan Ozturk from Bilkent University (Turkey), and Suleyman Tosun from Ankara University (Turkey)

- Workshop on Numerical Algorithms on Hybrid Architectures organized by Przemysław Stpiczyński from the Maria Curie Skłodowska University (Poland), and Jerzy Waśniewski from the Technical University of Denmark

- Workshop on Models, Algorithms and Methodologies for Hierarchical Parallelism in New HPC Systems organized by Giulliano Laccetti and Marco Lapegna from the University of Naples Federico II (Italy), and Raffaele Montella from the University of Naples Parthenope (Italy)

- Workshop on Power and Energy Aspects of Computation organized by Richard W.

Vuduc from the Georgia Institute of Technology (USA), Piotr Luszczek from the University of Tennessee (USA), and Leonel Sousa from the Technical University of Lisbon (Portugal)

- Workshop on Scheduling for Parallel Computing, SPC 2013, organized by Maciej Drozdowski from Poznań University of Technology (Poland)

- The 5th Workshop on Language-Based Parallel Programming Models, WLPP 2013, organized by Ami Marowka from the Bar-Ilan University (Israel)

- The 4th Workshop on Performance Evaluation of Parallel Applications on Large-Scale Systems organized by Jan Kwiatkowski from Wrocław University of Technology (Poland)

- Workshop on Parallel Computational Biology, PBC 2013, organized by David A.

Bader from the Georgia Institute of Technology (USA), Jarosław Żola from Rutgers University (USA), and Bertil Schmidt from the University of Mainz (Germany)

- Minisymposium on Applications of Parallel Computations in Industry and Engineering organized by Raimondas Čiegis from Vilnius Gediminas Technical University (Lithuania), and Julius Žilinskas from Vilnius University (Lithuania)

- Minisymposium on HPC Applications in Physical Sciences organized by Grzegorz Kamieniarz and Wojciech Florek from A. Mickiewicz University in Poznań (Poland)

- Minisymposium on Applied High-Performance Numerical Algorithms in PDEs organized by Piotr Krzyżanowski and Leszek Marcinkowski from Warsaw University (Poland), and Talal Rahman from Bergen University College (Norway)

- Minisymposium on High-Performance Computing Interval Methods organized by Bartłomiej J. Kubica from Warsaw University of Technology (Poland)

- Workshop on Complex Colective Systems organized by Paweł Topa and Jarosław Wąs from AGH University of Science and Technology in Kraków (Poland)

The PPAM 2013 meeting began with five tutorials:

- Scientific Computing on GPUs, by Dominik Göddeke from the University of Dortmund (Germany), and Robert Strzodka from NVIDIA

- Design and Implementation of Parallel Algorithms for Highly Heterogeneous HPC Platforms, by Alexey Lastovetsky from University College Dublin (Ireland)

- Node Level Performance Engineering, by Georg Hager from the University of Erlangen-Nuremberg (Germany)

- Delivering the OpenCl Performance Promise: Creating and Optimizing OpenCl Applications with the Intel OpenCl SDK, by Maxim Shevtsov from Intel (Russia)

- A History of A Central Result of Linear Algebra and the Role of that Gauss, Cholesky and Others Played in Its Development, by Fred Gustavson from the IBM T.J. Watson Research Center (USA)

The PPAM Best Poster Award is granted to the best poster on display at the PPAM conferences, and was established at PPAM 2009. This award is bestowed by the Program Committee members to the presenting author(s) of the best poster. The selection criteria are based on the scientific content, and on the quality of the poster presentation. The PPAM 2013 winners were Lars Karlsson, and Carl Christian K. Mikkelsen from Umea University, who presented the poster "Improving Perfect Parallelism." The Special Award was bestowed to Lukasz Szustak, and Krzysztof Rojek from the Częstochowa University of Technology, and Pawel Gepner from Intel, who presented the poster "Using Intel Xeon Phi to Accelerate Computation in MPDATA Algorithm."

A new topic was introduced at PPAM 2013: *Power and Energy Aspects of Computation (PEAC)*. Recent advances in computer hardware rendered the issues related to power and energy consumption as the driving metric for the design of computational platforms for years to come. Power-conscious designs, including multicore CPUs and various accelerators, dominate large supercomputing installations as well as large industrial complexes devoted to cloud computing and the big data analytics. At stake are serious financial and environmental impacts, which the large-scale computing community has to now consider and embark on careful re-engineering of software to fit the demanding power caps and tight energy budgets.

The workshop presented research into new ways of addressing these pressing issues of energy preservation, power consumption, and heat dissipation while attaining the best possible performance levels at the scale demanded by modern scientific challenges. The PEAC Workshop, as well as the conference as a whole, featured a number of invited and contributed talks covering a diverse array of recent advances, including:

- Cache-aware roofline model for monitoring performance and power in connection with application characterization (by L. Sousa et al.)

- Resource scheduling and allocation schemes based on stochastic models (by M. Oxley et al.)

- A comprehensive study of iterative solvers on a large variety of computing platforms including modern CPUs, accelerators, and embedded computers (by Enrique S. Quintana-Ortí et al.)

- Energy and power consumption trends in HPC (by P. Luszczek)

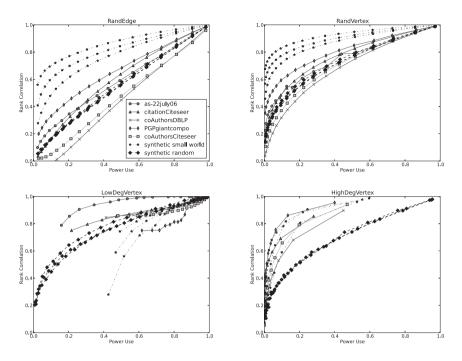

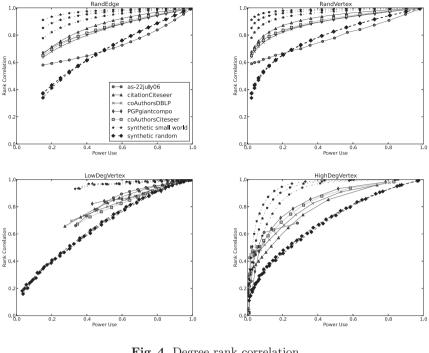

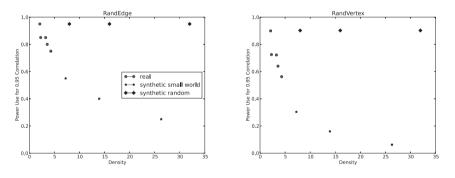

- Sensitivity of graph metrics to missing data and the benefits they have for overall energy consumption (by A. Zakrzewska et al.)

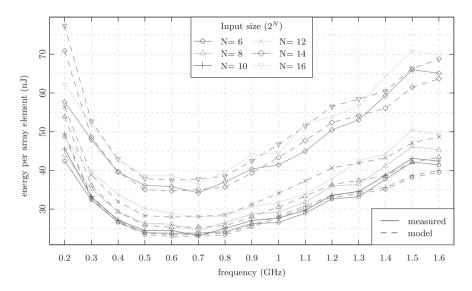

- Cache energy models and their analytical properties in the context of embedded devices (by K. de Vogeleer et al.)

- Predictive models for execution time, energy consumption, and power draw of algorithms (by R. Vuduc)

The organizers are indebted to the PPAM 2013 sponsors, whose support was vital to the success of the conference. The main sponsor was the Intel Corporation. The other sponsors were: IBM Corporation, Hewlett-Packard Company, Rogue Wave Software, and AMD. We thank to all the members of the international Program Committee and additional reviewers for their diligent work in refereeing the submitted papers. Finally, we thank all of the local organizers from the Częstochowa University of Technology, and the Polish-Japanese Institute of Information Technology in Warsaw, who helped us to run the event very smoothly. We are especially indebted to Grażyna Kołakowska, Urszula Kroczewska, Łukasz Kuczyński, Adam Tomaś, and Marcin Woźniak from the Częstochowa University of Technology; and to Jerzy P. Nowacki, Marek Tudruj, Jan Jedliński, and Adam Smyk from the Polish-Japanese Institute of Information Technology.

We hope that this volume will be useful to you. We would like everyone who reads it to feel invited to the next conference, PPAM 2015, which will be held September 6–9, 2015, in Kraków, the old capital of Poland.

January 2014

Roman Wyrzykowski Jack Dongarra Konrad Karczewski Jerzy Waśniewski

## Organization

#### **Program Committee**

Jan Węglarz Roman Wyrzykowski Ewa Deelman Francisco Almeida Pedro Alonso Peter Arbenz Piotr Bała David A. Bader Michael Bader

Włodzimierz Bielecki

Paolo Bientinesi Radim Blaheta Jacek Błażewicz Adam Bokota Pascal Bouvry Tadeusz Burczyński Jerzy Brzeziński Marian Bubak

Christopher Carothers Jesus Carretero Raimondas Čiegis

Andrea Clematis Jose Cunha Zbigniew Czech Jack Dongarra

Maciej Drozdowski Erik Elmroth Mariusz Flasiński Franz Franchetti Tomas Fryza Pawel Gepner

Poznań University of Technology, Poland (Honorary Chair) Częstochowa University of Technology, Poland (Program Committee Chair) University of Southern California, USA (Program Committee Vice-Chair) Universidad de La Laguna, Spain Universidad Politecnica de Valencia, Spain ETH. Zurich. Switzerland Nicolaus Copernicus University, Poland Georgia Institute of Technology, USA TU München, Germany West Pomeranian University of Technology, Poland **RWTH** Aachen, Germany Institute of Geonics, Czech Academy of Sciences Poznań University of Technology, Poland Częstochowa University of Technology, Poland University of Luxembourg Silesia University of Technology, Poland Poznań University of Technology, Poland AGH Kraków, Poland, and University of Amsterdam, The Netherlands Rensselaer Polytechnic Institute, USA Universidad Carlos III de Madrid, Spain Vilnius Gediminas Technical University, Lithuania IMATI-CNR, Italy University Nova of Lisbon, Portugal Silesia University of Technology, Poland University of Tennessee and ORNL, USA, and University of Manchester, UK Poznań University of Technology, Poland Umea University, Sweden Jagiellonian University, Poland Carnegie Mellon University, USA Brno University of Technology, Czech Republic Intel Corporation

Domingo Gimenez Mathieu Giraud Jacek Gondzio Andrzej Gościński Laura Grigori Adam Grzech Inge Gutheil Georg Hager José R. Herrero Ladislav Hluchy Florin Isaila Ondrei Jakl Emmanuel Jeannot Bo Kågström Alexey Kalinov Aneta Karaivanova Eleni Karatza Ayse Kiper Jacek Kitowski Jozef Korbicz Stanislaw Kozielski Dieter Kranzlmueller Henryk Krawczyk Piotr Krzyżanowski Mirosław Kurkowski Krzysztof Kurowski Jan Kwiatkowski Jakub Kurzak Giulliano Laccetti Marco Lapegna Alexey Lastovetsky Joao Lourenco Hatem Ltaief Emilio Luque Vyacheslav I. Maksimov Victor E. Malyshkin Pierre Manneback Tomas Margalef Svetozar Margenov Ami Marowka Norbert Meyer Jarek Nabrzyski Raymond Namyst Maya G. Neytcheva

University of Murcia, Spain LIFL and Inria, France University of Edinburgh, UK Deakin University, Australia Inria. France Wroclaw University of Technology, Poland Forschungszentrum Juelich, Germany University of Erlangen-Nuremberg, Germany Universitat Politecnica de Catalunva, Barcelona, Spain Slovak Academy of Sciences, Slovakia Universidad Carlos III de Madrid, Spain Institute of Geonics, Czech Academy of Sciences Inria, France Umea University, Sweden Cadence Design System, Russia Bulgarian Academy of Sciences, Sofia Aristotle University of Thessaloniki, Greece Middle East Technical University, Turkey Institute of Computer Science, AGH, Poland University of Zielona Góra, Poland Silesia University of Technology, Poland Ludwig Maximillian University, Munich, and Leibniz Supercomputing Centre, Germany Gdańsk University of Technology, Poland University of Warsaw, Poland Częstochowa University of Technology, Poland PSNC, Poznań, Poland Wrocław University of Technology, Poland University of Tennessee, USA University of Naples Federico II, Italy University of Naples Federico II, Italy University College Dublin, Ireland University Nova of Lisbon, Portugal KAUST, Saudi Arabia Universitat Autonoma de Barcelona, Spain Ural Branch, Russian Academy of Sciences Siberian Branch, Russian Academy of Sciences University of Mons, Belgium Universitat Autonoma de Barcelona, Spain Bulgarian Academy of Sciences, Sofia Bar-Ilan University, Israel PSNC, Poznań, Poland University of Notre Dame, USA University of Bordeaux and Inria, France Uppsala University, Sweden

Gabriel Oksa Ozcan Ozturk Tomasz Olas Marcin Paprzycki Dana Petcu Enrique S. Quintana-Ortí Jean-Marc Pierson Thomas Rauber Paul Renaud-Goud Jacek Rokicki Gudula Runger Leszek Rutkowski **Robert Schaefer Olaf Schenk** Stanislav Sedukhin Franciszek Seredyński Happy Sithole Jurij Silc Karolj Skala Peter M.A. Sloot Leonel Sousa Radek Stompor Przemysław Stpiczyński Maciei Stroiński Ireneusz Szcześniak Boleslaw Szymanski Domenico Talia Christian Terboven Andrei Tchernykh Suleyman Tosun Roman Trobec Denis Trystram Marek Tudruj Bora Uçar Marian Vajtersic Jerzy Waśniewski Bogdan Wiszniewski Andrzej Wyszogrodzki Ramin Yahyapour

Jianping Zhu Julius Žilinskas Jarosław Żola

Slovak Academy of Sciences, Bratislava Bilkent University, Turkey Częstochowa University of Technology, Poland IBS PAN and SWPS, Warsaw, Poland West University of Timisoara, Romania Universidad Jaime I, Spain Paul Sabatier University, France University of Bayreuth, Germany Inria. France Warsaw University of Technology, Poland Chemnitz University of Technology, Germany Czestochowa University of Technology, Poland Institute of Computer Science, AGH, Poland Università della Svizzera Italiana, Switzerland University of Aizu, Japan Cardinal Stefan Wyszyński University in Warsaw, Poland Centre for High Performance Computing, South Africa Jozef Stefan Institute, Slovenia Ruder Boskovic Institute, Croatia University of Amsterdam, The Netherlands Technical University of Lisbon, Portugal Université Paris Diderot and CNRS, France Maria Curie Skłodowska University, Poland PSNC, Poznań, Poland Częstochowa University of Technology, Poland Rensselaer Polytechnic Institute, USA University of Calabria, Italy RWTH Aachen, Germany CICESE Research Center, Ensenada, Mexico Ankara University, Turkey Jozef Stefan Institute, Slovenia Grenoble Institute of Technology, France Polish Academy of Sciences and Polish-Japanese Institute of Information Technology, Warsaw, Poland Ecole Normale Superieure de Lyon, France Salzburg University, Austria Technical University of Denmark Gdańsk University of Technology, Poland IMGW, Warsaw, Poland University of Göttingen/GWDG, Germany Cleveland State University, USA Vilnius University, Lithuania Rutgers University, USA

# **Contents – Part I**

| Algebra and Geometry Combined Explains How the Mind Does Math <i>Fred G. Gustavson</i>                                                      | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Numerical Algorithms and Parallel Scientific Computing                                                                                      |     |

| Exploiting Data Sparsity in Parallel Matrix Powers Computations<br>Nicholas Knight, Erin Carson, and James Demmel                           | 15  |

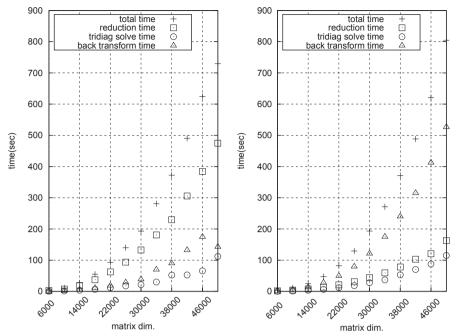

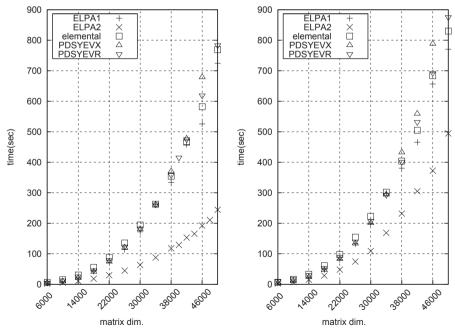

| Performance of Dense Eigensolvers on BlueGene/Q<br>Inge Gutheil, Jan Felix Münchhalfen, and Johannes Grotendorst                            | 26  |

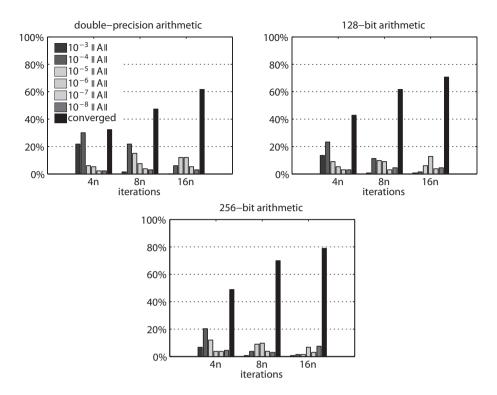

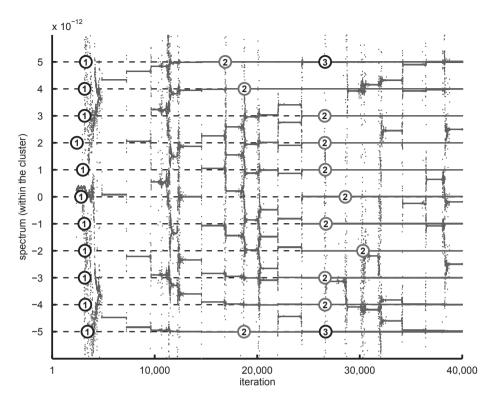

| Experiences with a Lanczos Eigensolver in High-Precision Arithmetic<br>Alexander Alperovich, Alex Druinsky, and Sivan Toledo                | 36  |

| Adaptive Load Balancing for Massively Parallel Multi-Level Monte<br>Carlo Solvers                                                           | 47  |

| Parallel One–Sided Jacobi SVD Algorithm with Variable Blocking Factor<br>Martin Bečka and Gabriel Okša                                      | 57  |

| An Identity Parareal Method for Temporal Parallel Computations<br>Toshiya Takami and Daiki Fukudome                                         | 67  |

| Improving Perfect Parallelism<br>Lars Karlsson, Carl Christian Kjelgaard Mikkelsen, and Bo Kågström                                         | 76  |

| Methods for High-Throughput Computation of Elementary Functions<br>Marat Dukhan and Richard Vuduc                                           | 86  |

| Engineering Nonlinear Pseudorandom Number Generators                                                                                        | 96  |

| Extending the Generalized Fermat Prime Number Search Beyond One Million<br>Digits Using GPUs<br><i>Iain Bethune and Michael Goetz</i>       | 106 |

| Iterative Solution of Singular Systems with Applications<br>Radim Blaheta, Ondřej Jakl, and Jiří Starý                                      | 114 |

| Statistical Estimates for the Conditioning of Linear Least Squares Problems<br>Marc Baboulin, Serge Gratton, Rémi Lacroix, and Alan J. Laub | 124 |

| Numerical Treatment of a Cross-Diffusion Model of Biofilm<br>Exposure to Antimicrobials                                                                             | 134 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Performance Analysis for Stencil-Based 3D MPDATA Algorithm<br>on GPU Architecture                                                                                   | 145 |

| Elliptic Solver Performance Evaluation on Modern Hardware Architectures<br>Milosz Ciznicki, Piotr Kopta, Michal Kulczewski, Krzysztof Kurowski,<br>and Pawel Gepner | 155 |

| Parallel Geometric Multigrid Preconditioner for 3D FEM in NuscaS<br>Software Package                                                                                | 166 |

| Scalable Parallel Generation of Very Large Sparse Benchmark Matrices<br>Daniel Langr, Ivan Šimeček, Pavel Tvrdík, and Tomáš Dytrych                                 | 178 |

| Parallel Non-Numerical Algorithms                                                                                                                                   |     |

| Co-operation Schemes for the Parallel Memetic Algorithm<br>Jakub Nalepa, Miroslaw Blocho, and Zbigniew J. Czech                                                     | 191 |

| Scalable and Efficient Parallel Selection Christian Siebert                                                                                                         | 202 |

| Optimal Diffusion for Load Balancing in Heterogeneous Networks<br>Katerina A. Dimitrakopoulou and Nikolaos M. Missirlis                                             | 214 |

| Parallel Bounded Model Checking of Security Protocols                                                                                                               | 224 |

| Tools and Environments for Parallel/Distributed/Cloud Computing                                                                                                     |     |

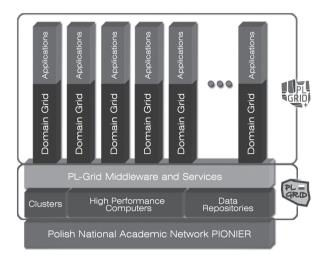

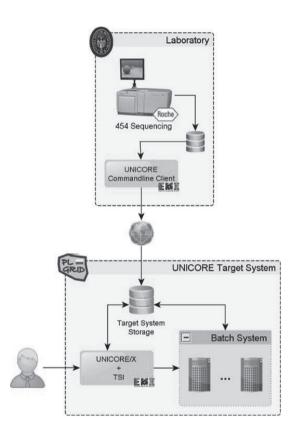

| Development of Domain-Specific Solutions Within the Polish Infrastructure<br>for Advanced Scientific Research                                                       | 237 |

| Cost Optimization of Execution of Multi-level Deadline-Constrained<br>Scientific Workflows on Clouds                                                                | 251 |

| Scientific Workflows on Clouds                             | 251 |

|------------------------------------------------------------|-----|

| Maciej Malawski, Kamil Figiela, Marian Bubak, Ewa Deelman, |     |

| and Jarek Nabrzyski                                        |     |

| Parallel Computations in the Volunteer–Based Comcute System<br>Paweł Czarnul, Jarosław Kuchta, and Mariusz Matuszek                                                                                               | 261 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

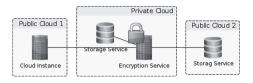

| Secure Storage and Processing of Confidential Data on Public Clouds<br>Jan Meizner, Marian Bubak, Maciej Malawski, and Piotr Nowakowski                                                                           | 272 |

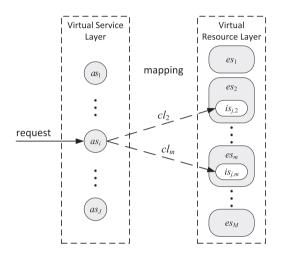

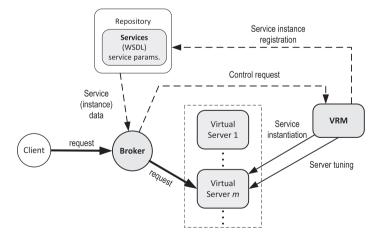

| Efficient Service Delivery in Complex Heterogeneous and Distributed<br>Environment                                                                                                                                | 283 |

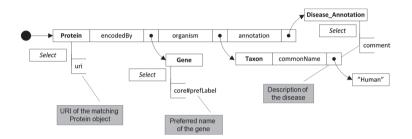

| Domain-Driven Visual Query Formulation over RDF Data Sets                                                                                                                                                         | 293 |

| Distributed Program Execution Control Based on Application Global<br>States Monitoring in PEGASUS DA Framework<br>Damian Kopański, Łukasz Maśko, Eryk Laskowski, Adam Smyk,<br>Janusz Borkowski, and Marek Tudruj | 302 |

| Application of Parallel Computing                                                                                                                                                                                 |     |

| New Scalable SIMD-Based Ray Caster Implementation for Virtual Machining<br>Alexander Leutgeb, Torsten Welsch, and Michael Hava                                                                                    | 317 |

| Parallelization of Permuting XML Compressors                                                                                                                                                                      | 327 |

| Parallel Processing Model for Syntactic Pattern Recognition-Based Electrical<br>Load Forecast                                                                                                                     | 338 |

| Parallel Event–Driven Simulation Based on Application Global<br>State Monitoring<br>Łukasz Maśko and Marek Tudruj                                                                                                 | 348 |

| Applied Mathematics, Evolutionary Computing and Metaheuristics                                                                                                                                                    |     |

| It's Not a Bug, It's a Feature: Wait-Free Asynchronous Cellular Genetic<br>Algorithm<br><i>Frédéric Pinel, Bernabé Dorronsoro, Pascal Bouvry, and Samee U. Khan</i>                                               | 361 |

| Genetic Programming in Automatic Discovery of Relationships in Computer<br>System Monitoring Data                                                                                                                 | 371 |

| Genetic Algorithms Execution Control Under a Global Application State<br>Monitoring Infrastructure                                                                                                                | 381 |

| Evolutionary Algorithms for Abstract Planning<br>Jaroslaw Skaruz, Artur Niewiadomski, and Wojciech Penczek                                                         | 392 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Solution of the Inverse Continuous Casting Problem with the Aid<br>of Modified Harmony Search Algorithm<br><i>Edyta Hetmaniok, Damian Stota, and Adam Zielonka</i> | 402 |

| Influence of a Topology of a Spring Network on its Ability to Learn<br>Mechanical Behaviour<br>Maja Czoków and Jacek Miękisz                                       | 412 |

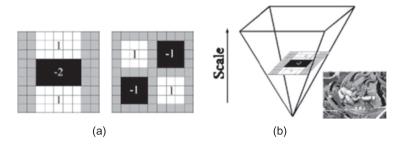

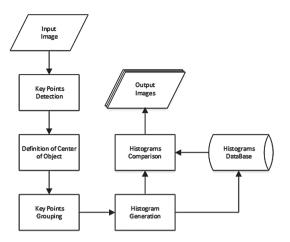

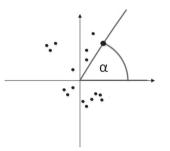

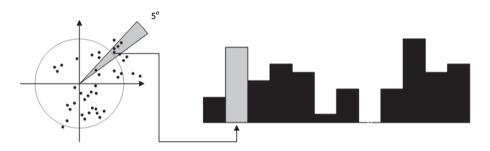

| Comparing Images Based on Histograms of Local Interest Points<br>Tomasz Nowak, Marcin Gabryel, Marcin Korytkowski, and Rafał Scherer                               | 423 |

| Improved Digital Image Segmentation Based on Stereo Vision and Mean<br>Shift Algorithm                                                                             | 433 |

### Minisymposium on GPU Computing

| Evaluation of Autoparallelization Toolkits for Commodity GPUs<br>David Williams, Valeriu Codreanu, Po Yang, Baoquan Liu, Feng Dong,<br>Burhan Yasar, Babak Mahdian, Alessandro Chiarini, Xia Zhao,<br>and Jos B.T.M. Roerdink | 447 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Real-Time Multiview Human Body Tracking Using GPU-Accelerated PSO<br>Boguslaw Rymut and Bogdan Kwolek                                                                                                                         | 458 |

| Implementation of a Heterogeneous Image Reconstruction System forClinical Magnetic ResonanceGrzegorz Tomasz Kowalik, Jennifer Anne Steeden, David Atkinson,Andrew Taylor, and Vivek Muthurangu                                | 469 |

| X-Ray Laser Imaging of Biomolecules Using Multiple GPUs<br>Stefan Engblom and Jing Liu                                                                                                                                        | 480 |

| Out-of-Core Solution of Eigenproblems for Macromolecular Simulations José I. Aliaga, Davor Davidović, and Enrique S. Quintana-Ortí                                                                                            | 490 |

| Using GPUs for Parallel Stencil Computations in Relativistic<br>Hydrodynamic Simulation                                                                                                                                       | 500 |

### Special Session on Multicore Systems

| PDNOC: An Efficient Partially Diagonal Network-on-Chip Design<br>Thomas Canhao Xu, Ville Leppänen, Pasi Liljeberg, Juha Plosila,<br>and Hannu Tenhunen                                                     | 513 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Adaptive Fork-Heuristics for Software Thread-Level Speculation                                                                                                                                             | 523 |

| Inexact Sparse Matrix Vector Multiplication in Krylov Subspace Methods:<br>An Application-Oriented Reduction Method                                                                                        | 534 |

| The Regular Expression Matching Algorithm for the Energy Efficient<br>Reconfigurable SoC<br>Paweł Russek and Kazimierz Wiatr                                                                               | 545 |

| Workshop on Numerical Algorithms on Hybrid Architectures                                                                                                                                                   |     |

| Performance Evaluation of Sparse Matrix Multiplication Kernels on<br>Intel Xeon Phi                                                                                                                        | 559 |

| Portable HPC Programming on Intel Many-Integrated-Core Hardware with<br>MAGMA Port to Xeon Phi<br>Jack Dongarra, Mark Gates, Azzam Haidar, Yulu Jia, Khairul Kabir,<br>Piotr Luszczek, and Stanimire Tomov | 571 |

| Using Intel Xeon Phi Coprocessor to Accelerate Computations in<br>MPDATA Algorithm                                                                                                                         | 582 |

| Accelerating a Massively Parallel Numerical Simulation in Electromagnetism<br>Using a Cluster of GPUs                                                                                                      | 593 |

| Multidimensional Monte Carlo Integration on Clusters with Hybrid<br>GPU-Accelerated Nodes                                                                                                                  | 603 |

| Efficient Execution of Erasure Codes on AMD APU Architecture<br>Roman Wyrzykowski, Marcin Woźniak, and Lukasz Kuczyński                                                                                    | 613 |

| AVX Acceleration of DD Arithmetic Between a Sparse Matrix and Vector<br><i>Toshiaki Hishinuma, Akihiro Fujii, Teruo Tanaka, and Hidehiko Hasegawa</i>                                                      | 622 |

| Using Quadruple Precision Arithmetic to Accelerate Krylov Subspace<br>Methods on GPUs.                                                                                                                               | 632 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Daichi Mukunoki and Daisuke Takahashi                                                                                                                                                                                |     |

| Effectiveness of Sparse Data Structure for Double-Double and<br>Quad-Double Arithmetics                                                                                                                              | 643 |

| Efficient Heuristic Adaptive Quadrature on GPUs: Design and Evaluation<br>Daniel Thuerck, Sven Widmer, Arjan Kuijper, and Michael Goesele                                                                            | 652 |

| An Efficient Representation on GPU for Transition Rate Matrices for<br>Markov Chains<br>Jarosław Bylina, Beata Bylina, and Marek Karwacki                                                                            | 663 |

| Eigen-G: GPU-Based Eigenvalue Solver for Real-Symmetric Dense Matrices<br>Toshiyuki Imamura, Susumu Yamada, and Masahiko Machida                                                                                     | 673 |

| A Square Block Format for Symmetric Band Matrices<br>Fred G. Gustavson, José R. Herrero, and Enric Morancho                                                                                                          | 683 |

| Workshop on Models, Algorithms, and Methodologies for Hierarchical<br>Parallelism in New HPC Systems                                                                                                                 |     |

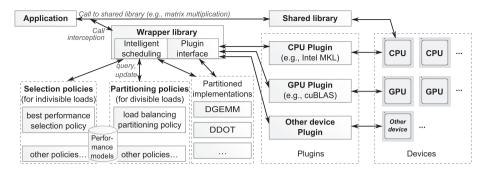

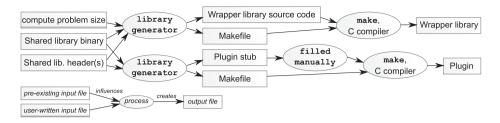

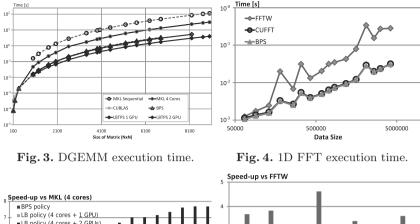

| Transparent Application Acceleration by Intelligent Scheduling of Shared<br>Library Calls on Heterogeneous Systems<br>João Colaço, Adrian Matoga, Aleksandar Ilic, Nuno Roma, Pedro Tomás,<br>and Ricardo Chaves     | 693 |

| A Study on Adaptive Algorithms for Numerical Quadrature on Heterogeneous<br>GPU and Multicore Based Systems                                                                                                          | 704 |

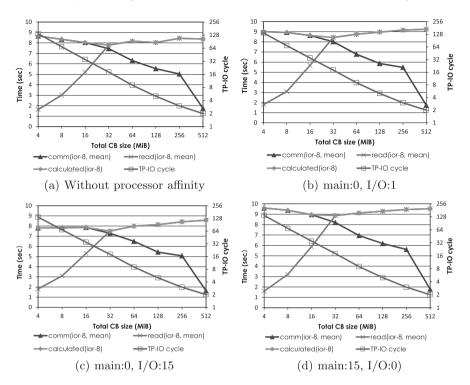

| Improving Parallel I/O Performance Using Multithreaded Two-Phase I/O<br>with Processor Affinity Management                                                                                                           | 714 |

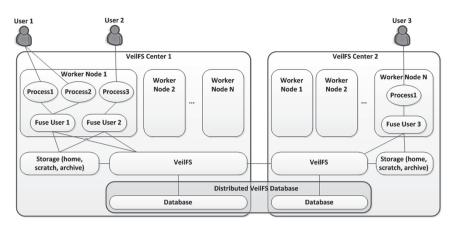

| Storage Management Systems for Organizationally Distributed Environments<br>PLGrid PLUS Case Study<br>Renata Słota, Łukasz Dutka, Michał Wrzeszcz, Bartosz Kryza,<br>Darin Nikolow, Dariusz Król, and Jacek Kitowski | 724 |

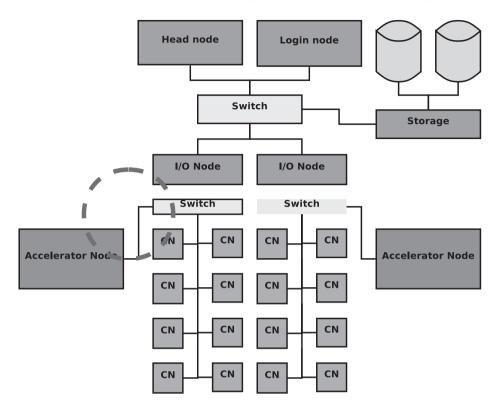

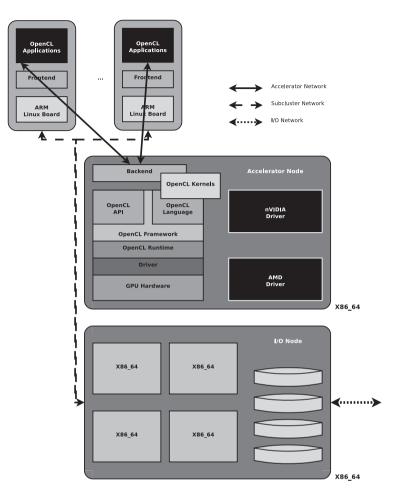

| The High Performance Internet of Things: Using GVirtuS to Share High-End GPUs with ARM Based Cluster Computing Nodes<br>Giuliano Laccetti, Raffaele Montella, Carlo Palmieri,<br>and Valentina Pelliccia             | 734 |

## Workshop on Power and Energy Aspects of Computation

| Monitoring Performance and Power for Application Characterization<br>with the Cache-Aware Roofline Model<br><i>Diogo Antão, Luís Taniça, Aleksandar Ilic, Frederico Pratas,</i><br><i>Pedro Tomás, and Leonel Sousa</i>                                         | 747 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Energy and Deadline Constrained Robust Stochastic Static Resource Allocation<br>Mark A. Oxley, Sudeep Pasricha, Howard Jay Siegel,<br>and Anthony A. Maciejewski                                                                                                | 761 |

| Performance and Energy Analysis of the Iterative Solution of Sparse Linear<br>Systems on Multicore and Manycore Architectures<br>José I. Aliaga, Hartwig Anzt, Maribel Castillo, Juan C. Fernández,<br>Germán León, Joaquín Pérez, and Enrique S. Quintana-Ortí | 772 |

| Measuring the Sensitivity of Graph Metrics to Missing Data<br>Anita Zakrzewska and David A. Bader                                                                                                                                                               | 783 |

| The Energy/Frequency Convexity Rule: Modeling and Experimental<br>Validation on Mobile Devices                                                                                                                                                                  | 793 |

| Author Index                                                                                                                                                                                                                                                    | 805 |

# **Contents – Part II**

| Workshop on Scheduling for Parallel Computing (SPC 2013)                                                                                |     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Scheduling Bag-of-Tasks Applications to Optimize Computation<br>Time and Cost                                                           | 3   |

| Scheduling Moldable Tasks with Precedence Constraints and Arbitrary<br>Speedup Functions on Multiprocessors<br>Sascha Hunold            | 13  |

| OStrich: Fair Scheduling for Multiple Submissions<br>Joseph Emeras, Vinicius Pinheiro, Krzysztof Rzadca, and Denis Trystram             | 26  |

| Fair Share Is Not Enough: Measuring Fairness in Scheduling<br>with Cooperative Game Theory<br><i>Piotr Skowron and Krzysztof Rzadca</i> | 38  |

| Setting up Clusters of Computing Units to Process Several Data Streams<br>Efficiently<br>Daniel Millot and Christian Parrot             | 49  |

| The 5th Workshop on Language-Based Parallel Programming Models (WLPP 2013)                                                              |     |

| Towards Standardization of Measuring the Usability of Parallel Languages<br>Ami Marowka                                                 | 65  |

| Experiences with Implementing Task Pools in Chapel and X10<br>Claudia Fohry and Jens Breitbart                                          | 75  |

| Parampl: A Simple Approach for Parallel Execution of AMPL Programs<br>Artur Olszak and Andrzej Karbowski                                | 86  |

| Prototyping Framework for Parallel Numerical Computations<br>Ondřej Meca, Stanislav Böhm, Marek Běhálek, and Martin Šurkovský           | 95  |

| Algorithms for In-Place Matrix Transposition                                                                                            | 105 |

| FooPar: A Functional Object Oriented Parallel Framework in Scala <i>Felix Palludan Hargreaves and Daniel Merkle</i>                     | 118 |

| Effects of Segmented Finite Difference Time Domain on GPU<br>Jose Juan Mijares Chan, Gagan Battoo, Parimala Thulasiraman,<br>and Ruppa K. Thulasiram           | 130 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Optimization of an OpenCL-Based Multi-swarm PSO Algorithm on an APU Wayne Franz, Parimala Thulasiraman, and Ruppa K. Thulasiram                                | 140 |

| Core Allocation Policies on Multicore Platforms to Accelerate Forest<br>Fire Spread Predictions                                                                | 151 |

| The 4th Workshop on Performance Evaluation of Parallel Applications on Large-Scale Systems                                                                     |     |

| The Effect of Parallelization on a Tetrahedral Mesh Optimization Method<br>Domingo Benitez, Eduardo Rodríguez, José M. Escobar,<br>and Rafael Montenegro       | 163 |

| Analysis of Partitioning Models and Metrics in Parallel Sparse<br>Matrix-Vector Multiplication<br><i>Kamer Kaya, Bora Uçar, and Ümit V. Catalyürek</i>         | 174 |

| Achieving Memory Scalability in the GYSELA Code to Fit Exascale<br>Constraints<br>Fabien Rozar, Guillaume Latu, and Jean Roman                                 | 185 |

| Probabilistic Analysis of Barrier Eliminating Method Applied<br>to Load-Imbalanced Parallel Application                                                        | 196 |

| Multi-GPU Parallel Memetic Algorithm for Capacitated Vehicle Routing<br>Problem<br>Mieczysław Wodecki, Wojciech Bożejko, Michał Karpiński,<br>and Maciej Pacut | 207 |

| Parallel Applications Performance Evaluation Using the Concept<br>of Granularity                                                                               | 215 |

| Workshop on Parallel Computational Biology (PBC 2013)                                                                                                          |     |

| Resolving Load Balancing Issues in BWA on NUMA Multicore<br>Architectures                                                                                      | 227 |

| K-mulus: Strategies for BLAST in the Cloud<br>Christopher M. Hill, Carl H. Albach, Sebastian G. Angel, and Mihai Pop                                           | 237 |

| Faster GPU-Accelerated Smith-Waterman Algorithm with Alignment<br>Backtracking for Short DNA Sequences                                                                                                            | 247       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Accelerating String Matching on MIC Architecture for Motif Extraction<br>Solon P. Pissis, Christian Goll, Pavlos Pavlidis, and Alexandros Stamatakis                                                              | 258       |

| A Parallel, Distributed-Memory Framework for Comparative<br>Motif Discovery                                                                                                                                       | 268       |

| Parallel Seed-Based Approach to Protein Structure Similarity Detection<br>Guillaume Chapuis, Mathilde Le Boudic - Jamin, Rumen Andonov,<br>Hristo Djidjev, and Dominique Lavenier                                 | 278       |

| Minisymposium on Applications of Parallel Computation<br>in Industry and Engineering                                                                                                                              |           |

| A Parallel Solver for the Time-Periodic Navier–Stokes Equations<br>Peter Arbenz, Daniel Hupp, and Dominik Obrist                                                                                                  | 291       |

| Parallel Numerical Algorithms for Simulation of Rectangular Waveguides<br>by Using GPU                                                                                                                            | 301<br>15 |

| OpenACC Parallelisation for Diffusion Problems, Applied<br>to Temperature Distribution on a Honeycomb Around the Bee Brood:<br>A Worked Example Using BiCGSTAB<br><i>Hermann J. Eberl and Rangarajan Sudarsan</i> | 311       |

| Application of CUDA for Acceleration of Calculations in Boundary Value<br>Problems Solving Using PIES<br>Andrzej Kuzelewski, Eugeniusz Zieniuk, and Agnieszka Boltuc                                              | 322       |

| Modeling and Simulations of Beam Stabilization in Edge-Emitting<br>Broad Area Semiconductor Devices<br><i>Mindaugas Radziunas and Raimondas Čiegis</i>                                                            | 332       |

| Concurrent Nomadic and Bundle Search: A Class of Parallel Algorithms<br>for Local Optimization                                                                                                                    | 343       |

| Parallel Multi-objective Memetic Algorithm for Competitive Facility<br>Location                                                                                                                                   | 354       |

| Parallelization of Encryption Algorithm Based on Chaos System<br>and Neural Networks<br>Dariusz Burak                                                                                                                             | 364      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Minisymposium on HPC Applications in Physical Sciences                                                                                                                                                                            |          |

| Simulations of the Adsorption Behavior of Dendrimers<br>Jarosław S. Kłos and Jens U. Sommer                                                                                                                                       | 377      |

| An Optimized Lattice Boltzmann Code for BlueGene/Q<br>Marcello Pivanti, Filippo Mantovani, Sebastiano Fabio Schifano,<br>Raffaele Tripiccione, and Luca Zenesini                                                                  | 385      |

| A Parallel and Scalable Iterative Solver for Sequences of Dense<br>Eigenproblems Arising in FLAPW<br>Mario Berljafa and Edoardo Di Napoli                                                                                         | 395      |

| Sequential Monte Carlo in Bayesian Assessment of Contaminant Source<br>Localization Based on the Sensors Concentration Measurements<br>Anna Wawrzynczak, Piotr Kopka, and Mieczyslaw Borysiewicz                                  | 407      |

| Effective Parallelization of Quantum Simulations: Nanomagnetic<br>Molecular Rings                                                                                                                                                 | 418      |

| DFT Study of the Cr <sub>8</sub> Molecular Magnet Within Chain-Model<br>Approximations                                                                                                                                            | 428<br>? |

| Non-perturbative Methods in Phenomenological Simulations<br>of Ring-Shape Molecular Nanomagnets<br>Piotr Kozłowski, Grzegorz Musiał, Monika Haglauer, Wojciech Florek,<br>Michał Antkowiak, Filippo Esposito, and Dante Gatteschi | 438      |

| Non-uniform Quantum Spin Chains: Simulations of Static<br>and Dynamic Properties                                                                                                                                                  | 448      |

| Minisymposium on Applied High Performance Numerical Algorithms in PI                                                                                                                                                              | DEs      |

| A Domain Decomposition Mathed for Discretization of Multiscale Elliptic                                                                                                                                                           |          |

| A Domain Decomposition Method for Discretization of Multiscale Elliptic |     |

|-------------------------------------------------------------------------|-----|

| Problems by Discontinuous Galerkin Method                               | 461 |

| Maksymilian Dryja                                                       |     |

| Parallel Preconditioner for the Finite Volume Element Discretization<br>of Elliptic Problems                                         | 469 |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Leszek Marcinkowski and Talal Rahman                                                                                                 |     |

| Preconditioning Iterative Substructuring Methods Using Inexact Local Solvers<br>Piotr Krzyzanowski                                   | 479 |

| Additive Schwarz Method for Nonsymmetric Local Discontinuous<br>Galerkin Discretization of Elliptic Problem<br><i>Filip Z. Klawe</i> | 489 |

| Fast Numerical Method for 2D Initial-Boundary Value Problems<br>for the Boltzmann Equation                                           | 499 |

| Simulating Phase Transition Dynamics on Non-trivial Domains                                                                          | 510 |

| Variable Block Multilevel Iterative Solution of General Sparse Linear<br>Systems                                                     | 520 |

| An Automatic Way of Finding Robust Elimination Trees for a Multi-frontal<br>Sparse Solver for Radical 2D Hierarchical Meshes         | 531 |

| Parallel Efficiency of an Adaptive, Dynamically Balanced Flow Solver<br>Stanislaw Gepner, Jerzy Majewski, and Jacek Rokicki          | 541 |

| Modification of the Newton's Method for the Simulations of Gallium<br>Nitride Semiconductor Devices                                  | 551 |

| Numerical Realization of the One-Dimensional Model of Burning Methanol<br>Krzysztof Moszyński                                        | 561 |

| Minisymposium on High Performance Computing Interval Methods                                                                         |     |

| A Shaving Method for Interval Linear Systems of Equations                                                                            | 573 |

| Finding Enclosures for Linear Systems Using Interval Matrix Multiplication<br>in CUDA                                                | 582 |

| GPU Acceleration of Metaheuristics Solving Large Scale Parametric<br>Interval Algebraic Systems<br>Jerzy Duda and Iwona Skalna                                           | 591 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Parallel Approach to Monte Carlo Simulation for Option Price Sensitivities<br>Using the Adjoint and Interval Analysis<br>Grzegorz Kozikowski and Bartłomiej Jacek Kubica | 600 |

| Subsquares Approach – A Simple Scheme for Solving Overdetermined<br>Interval Linear Systems<br>Jaroslav Horáček and Milan Hladík                                         | 613 |

| Using Quadratic Approximations in an Interval Method for Solving<br>Underdetermined and Well-Determined Nonlinear Systems                                                | 623 |

| The Definition of Interval-Valued Intuitionistic Fuzzy Sets<br>in the Framework of Dempster-Shafer Theory<br>Ludmila Dymova and Pavel Sevastjanov                        | 634 |

| Interval Finite Difference Method for Solving the Problem of Bioheat<br>Transfer Between Blood Vessel and Tissue                                                         | 644 |

| Workshop on Complex Collective Systems                                                                                                                                   |     |

| Bridging the Gap: From Cellular Automata to Differential Equation Models<br>for Pedestrian Dynamics                                                                      | 659 |

| Cellular Model of Pedestrian Dynamics with Adaptive Time Span                                                                                                            | 669 |

| The Use of GPGPU in Continuous and Discrete Models of Crowd Dynamics<br>Hubert Mróz, Jarosław Wąs, and Paweł Topa                                                        | 679 |

| Modeling Behavioral Traits of Employees in a Workplace with Cellular<br>Automata<br>Petros Saravakos and Georgios Ch. Sirakoulis                                         | 689 |

| Probabilistic Pharmaceutical Modelling: A Comparison Between<br>Synchronous and Asynchronous Cellular Automata                                                           | 699 |

| The Graph of Cellular Automata Applied for Modelling Tumour<br>Induced Angiogenesis<br>Paweł Topa                                                                        | 711 |

| Neighborhood Selection and Rules Identification for Cellular Automata:<br>A Rough Sets Approach<br>Bartłomiej Płaczek                                    | 721 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Coupling Lattice Boltzmann Gas and Level Set Method for Simulating<br>Free Surface Flow in GPU/CUDA Environment<br><i>Tomir Kryza and Witold Dzwinel</i> | 731 |

| Creation of Agent's Vision of Social Network Through Episodic Memory<br>Michał Wrzeszcz and Jacek Kitowski                                               | 741 |

| The Influence of Multi-agent Cooperation on the Efficiency<br>of Taxi Dispatching                                                                        | 751 |

| Basic Endogenous-Money Economy: An Agent-Based Approach<br>Ivan Blecic, Arnaldo Cecchini, and Giuseppe A. Trunfio                                        | 761 |

| Author Index                                                                                                                                             | 771 |

## Algebra and Geometry Combined Explains How the Mind Does Math

Fred G. Gustavson<sup>1,2</sup>  $(\boxtimes)$

<sup>1</sup> IBM T.J. Watson Research Center, Ossining, USA <sup>2</sup> Umeå University, Umeå, Sweden fg2935@gmail.com

Abstract. This paper updates my talk on Cache Blocking for Dense Linear Algorithms since 1985 given at PPAM 11; see [11]. We again apply Dimension Theory to matrices in the Fortran and C programming languages. New Data Structures (**NDS**) for matrices are given. We use the GCD algorithm to transpose a n by m matrix A in CMO order, standard layout, in-place. Algebra and Geometry are used to make this idea concrete and practical; it is the reason for title of our paper: make a picture of any matrix by the GCD algorithm to convert it into direct sum of square submatrices. The picture is Geometry and the GCD algorithm is Algebra. Also, the in-place transposition of the GKK and TT algorithms will be compared. Finally, the importance of using negative integers will be used to give new results about subtraction and finding primitive roots which also make a priori in-place transpose more efficient.

**Keywords:** New data structures  $(NDS) \cdot$  In-place matrix transposition  $\cdot$  Cache blocking  $\cdot$  Dimension theory  $\cdot$  Negative integers

#### 1 Introduction

This paper updates research about **NDS** that were given at PPAM 11 [11] and so we just overview [11] to make this paper cogent and self-contained. We claim that partitioning matrices into disjoint submatices using **NDS** is very important for DLA (**D**ense **L**inear **A**lgebra). The standard matrix data layouts, column and row major order, (CMO and RMO) are **very unlikely** to change. Hence, submatrices must be reformatted so that moving them between memory and caches allow them to benefit from the principles underlying cache blocking. In this regard, the concluding summary of [11] said: We indicated [3,4] that DLAFA (**F**actorization **A**lgorithms) are mainly MM (**M**atrix **M**ultiply) algorithms. The standard API, **A** Programming Interface, for matrices and Level-3 BLAS use arrays; see page 739 of [2]. All standard array layouts are *one* dimensional. It is *impossible* to maintain locality of reference in a matrix or any higher than 1-D object using a 1-D layout; see [19]. MM requires row and column operations and thus requires MT (**M**atrix **T**ransformation) to NDS. Our results on in-place MT show that performance suffers greatly when one uses a 1-D layout. Using NDS for matrices "approximates" a 2-D layout; thus, one can dramatically improve in-place MT performance as well as DLAFA performance. Our message is that DLAFA are mostly MM. MM requires MT and both require NDS. Thus, DLAFA can and do perform well on multicore but only if one uses NDS.

An application of the Algorithms and Architecture Approach [4] describes a "fundamental principle" of Linear Algebra called the "Principle of Linear Superposition". We use it to describe the factorization algorithms of DLA of a matrix A in terms of its sub matrices  $A_{ij}$  instead of its elements  $a_{ij}$ . These submatrices must be laid out optimally on a given platform to ensure automatic cache blocking! The LAPACK and ScaLAPACK libraries were also based on this fundamental principle. However, both of these libraries use standard data layouts for matrices and the Level-3 BLAS to gain their performance on all platforms. This decision worked until the introduction of Multi-Core, MC. Peak performance for DLA factorization only occurs if all matrix operands are used multiple times when they enter an L1 cache or core. This ensures that the initial cost of bringing an operand into cache is then amortized by the ratio of  $O(n^3)$  arithmetic to  $O(n^2)$  elements or **nb** flops<sup>1</sup> per matrix element  $a_{ij}$ . Multiple reuse of all operands *only* occurs if all matrix operands map well into the L1 caches. For MC processors, an "L1 cache" is the data area of a core. For MC it is critical to get submatrices to the cores as fast as possible. The standard programming interface, called API, that hold matrices A that the BLAS and DLA libraries use is the 2-D array of the Fortran and C programming languages. For this API, submatrices  $A_{ij}$  of A are not stored contiguously. Thus it is *impossible* to move  $A_{ij}$  to and from the memory hierarchy from and to the various cores in a fast or optimal manner! This problem is corrected by using NDS to hold these submatrices  $A_{ij}$ . By using dimension theory [19] we shall indicate why this is true.

For MC the disproportion between multiple CPU processing and memory speed has become much higher. On a negative side, the API for BLAS-3 hurts performance; it requires repeated matrix data reformatting from its API to NDS. A new "BLAS-3" concept has emerged; it is to use NDS in concert with "BLAS-3" kernels [1,4,16,17]. For MC, the broad idea of "cache blocking" is mandatory as matrix elements must be fed to SPE's or GPU's as fast as possible. Also important is the arrangement in memory of the submatrices  $A_{ij}$  of A that are to be processed. This then defines "cache blocking" on MC processors for DLA.

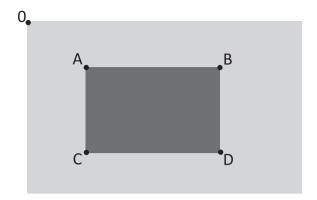

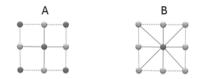

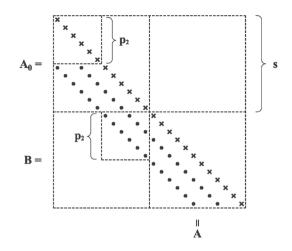

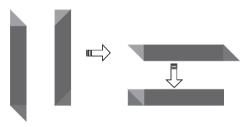

We describe three matrix layouts. First, we assume that the matrices are stored in Rectangular Block (RB) format. RB format stores a M by N matrix Aas contiguous rectangular submatrices  $A_{ij}$  of size MB by NB. Square Block (SB) format is a special case of RB format when the rectangle is a square. A SB of order NB is also a contiguous 1-D array of size NB<sup>2</sup> and for most cache designs a contiguous array whose size fits into the cache is mapped from its place in memory into the cache by the *identity* mapping. RB format has a number of other advantages. A major one is that it naturally partitions a matrix to be a matrix of sub-matrices. This allows one to view matrix transposition of a M by

<sup>&</sup>lt;sup>1</sup> **nb** is the order of a square submatrix  $A_{ij}$  of A that enters a core.

N matrix A where M = mMB and N = nNB as a **block transposition** of a much smaller m by n block matrix A. However, usually M and N are not multiples of MB and NB. So, RB format as we define it here, would pad the rows and columns of A so that M and N become multiples of some blocking factors MB and NB. We think padding is an **essential condition** for this type of "cache blocking".

The second format for storing matrices is the standard 2-D array format of the Fortran and C programming languages. The third format is defined by the GCD in-place transpose algorithm [6]. The two key ideas are "the GCD algorithm is used to represent any CMO matrix A as a direct sum of square submatices  $A_i$ " and "knowing any square matrix can be transposed in-place".

Section 2 gives a discussion of Dimension Theory. It describes the "random nature" of the memory layout of the standard API and thus shows why Fortran and C arrays *cannot* be truly multi-dimensional. Section 3 describes the features of In-Place Transformations between standard full layouts of matrices and the RB or square block SB formats of NDS. The key algorithm is "vector transpose": it demonstrate a novel form of "cache blocking" where CMO A is reorganized to be very efficient for DLA algorithms. Section 4 compares the in-place transposition algorithms of TT [13,20] and GKK [10]. Section 5 describes GCD transpose and Sect. 6 describes new results based on using negative integers.

#### 2 Dimension Theory and Its Relation to Standard CM and RM Arrays of Fortran and C

Fortran and C use 1-D layouts for their multi-dimensional arrays. Most library software for DLA use the Fortran and C API for their matrices which are clearly 2-D. The Fundamental Theorem of Dimension Theory states that it is *impossible* to preserve closeness of all points p in a neighborhood  $\mathcal{N}$  of a D dimensional object when one uses a d < D dimensional coordinate system to describe the object; see pages 106 to 120 of [19]. We are concerned with a submatrix  $A_{ij}$  which is representing a  $\mathcal{N}$  of a matrix A that is a 2-D object. The result says that it is *impossible* to lay out matrix A in a 1-D fashion and maintain closeness of all of the elements of  $A_{ij}$ . The result warns us about moving  $A_{ij}$  to and from cache as cache represents a  $\mathcal{N}$  of 2-D object A. Computer scientists use the phrase "preserve data locality" when data is mapped from memory into a cache and we note that when data  $A_{ij}$  is contiguous in computer memory then its mapping into cache is by the *identity* mapping. Clearly, this is the **fastest way to move data** and it also **preserves data locality** in cache.

#### 2.1 Submatrices $A_{ij}$ of A in Fortran and C and Their Generalization

Let A have m rows and n columns with  $LDA \ge m$ . In Fortran the columns of A are stored stride one and the row elements are stored LDA elements apart. This is a 1-D layout.  $A^T$  has n rows and m columns with  $LDAT \ge n$ . Its rows are stored stride one and its columns are laid out LDAT elements apart. Again, this is a 1-D layout. Actually A and  $A^T$  are the same object and this is how we "view" A or  $A^T$ . Clearly both A and  $A^T$  contain the same information. Now, everything we just said about A and  $A^T$  applies equally well to every submatrix  $A_{ij}$  of A and its transpose  $A_{ij}^T$ . However, copies of submatrices are usually made during the processing of DLA algorithms when A is in standard layout. To avoid this we generalize the layout of A to be RB format where each scalar  $a_{i,j}$  element of standard format becomes a rectangular or square submatrix A(I:I+MB-1, J:J+NB-1) of size MB rows and NB columns. All submatrices are contiguous, meaning LDA = MB. Simple and non-simple layouts of A(I:I + MB - 1, J:J + NB - 1) are used; see Sect. 2.1 of [5] and [7] for the meaning of non-simple format. Today, these non-simple formats are called **rb** formats standing for register block formats. The last block rows and columns of RB Aare called left-over blocks. These  $A_{II}$  blocks reside in MB\*NB locations of array storage even though they require less storage to store. It is very important to pad these left-over blocks; otherwise the theory behind in-place fast data movement of RB A breaks down somewhat or becomes less efficient. With these changes one can transpose or transform RB A submatrices both in-place and out-of-place.

#### 2.2 Tutorial on the Essence of Dimension

We now return to our description of Dimension Theory. This is a deep mathematical subject and we think it sheds light on the subject of cache blocking. Before going further let us study 2-D domains; e.g. a matrix or a City Map. The concept to emerge is "closeness of *all* points in a neighborhood" of an arbitrary domain point p. How does one describe an arbitrary neighborhood? Here is the key question: when does a labeling of a domain satisfy the neighborhood property of closeness? This notion can be made mathematically precise and correct and so we can define dimension in a satisfactory manner.

Before answering we back up and try other labelings of domain points. Let us try natural Numbers:  $1, 2, 3, \ldots$ . Fortran and C use this labeling to lay out matrices A; e.g., in Fortran scalar element  $a_{ij}$  is located in computer memory at word location  $\mathbf{i} + (\mathbf{j} - 1) * \text{LDA}$  past the beginning word of A. Notice that some neighboring  $a_{ij}$  elements are widely separated with this single labeling; e.g., in Fortran CM format row elements are widely separated in memory by LDA elements. Is this true for all single labelings of 2-D objects? The answer is yes. Next we need to measure distance. We give a metric for a neighborhood that uses two coordinates. We use a one norm: let p = (u, v) and q = (x, y) be two points. Then  $\operatorname{norm}(p, q) = |u - x| + |v - y|$ .

We are now ready to give the mathematical essence of dimension. Indexing with single numbers, or simple enumeration is applicable only to those cases where the objects have the character of a sequence. Simple, single indexing must obey the neighborhood property and these objects are labeled one dimensional. Now consider maps, matrices, etc. and note they *cannot* be labeled by a simple sequential ordering as the "the neighborhood property will be violated" (we have said this was so above). However, two simple sequences suffice. The use of the one norm shows us why visually. Now we discuss some prior history about dimension and its resolution. There was an "erroneous prior notion" that a rectangle had more points than a line; and that a solid had more points than a rectangle! Later, Cantor's theory of infinities asserted that "All domains have the same number of points"! Thus this "erroneous prior notion" needed to be corrected. However, a difficult problem remained: "is it possible to label a domain with two different labelings that both obey the neighborhood principle of a higher to lower labeling"? The Fundamental Theorem of Dimension Theory says the answer is **no**! In 1913 L. E. J. Brouwer stated and proved this theorem which we now phrase in a slightly different manner. "It is *not* possible to label a domain with two different labelings that both obey the neighborhood principle".

#### 3 Converting Standard Format to RB Format In-Place via Vector Transposition

In [8] we demonstrated in-place transposition for matrices stored in CM format. In terms of speed they improved the existing state-of-the-art slightly. However, they were very slow compared to out-of-place transpose algorithms. There is no way to overcome this problem if one insists on storing A in a 1-D layout. Let  $M \times$ N matrix A be laid out in CM format. In Fortran we have A(0:M-1,0:N-1). The element  $a_{ij}$  is stored at offset k = i + jM or A[k] and the in-place permutation P(k) has  $a_{ij} = A[k]$  ending up at offset  $\bar{k} = i\mathbb{N} + j$  or at  $A[\bar{k}]$ . Note that P(k)also equals  $k\mathbb{N} \mod q$  where  $q = M\mathbb{N} - 1$  and so P(k) is governed by modular arithmetic. Now modular arithmetic with parameters  $\mathbb{N}$  and q also define different pseudo-random number generators; see [15, Section 3.2.1.3]. It follows that inplace transpose algorithms in Fortran and C will exhibit a random memory access pattern and thus have very poor performance: each memory access will likely miss in each level of the cache hierarchy. Cache miss penalties are huge (in the hundreds of cycles) for MC processors. This number theory above and dimension theory of Sect. 2, explaining poor performance, are conjectured to be related.

#### 3.1 Dense Linear Algebra Algorithms for MC Use RB or SB Format

We need a fast way to transform A, in a standard CM or RM format, to be in RB format [9,10,14]. The idea is to move contiguous lines of data. The VIPX algorithm of [9] maps in-place CM A residing in a Fortran array A(0:mMB-1,0:nNB-1)to be RB A also residing in A. A column swath is an mMB by NB subarray of A; we call it B(0:mMB-1,0:NB-1). The LDA's of both these array are LDA = mMB. Under the column swath vector mapping CM A becomes m size MB by NB RB's. Algorithm VIPX is embarrassingly parallel: it is applied n times on the n column swaths of A to produce RB A. Section 3.2 describes the VIPX algorithm. CM A and RB format A will occupy array A with LDA = mMB where  $m = \lceil M/MB \rceil$ ; see Sect. 2.1 where this layout padding was mentioned as being important. In [10] we improved the speed of the VIPX algorithm by using a number theory algorithm to find, a priori, the exact nature of the vector Pmapping.

#### 3.2 The VIPX Vector Transpose Algorithm

We overview how one gets from standard CM format to RB format. Recall, from Sect. 3.1, array B holds an m by NB submatrix C whose elements are column vectors of length MB. Let  $C^T$  also occupy array B.  $C^T$  is a size NB by m matrix of vectors of length MB. To see what is going on we give a small example. Let m = 4, MB=2 and NB=3. Then C, as a scalar matrix of size mMB = 8 by NB = 3, is also a m = 4 by NB = 3 matrix of vectors of length MB = 2 residing in array B. Originally, the mNB = 12 vectors of C are stored in CM format in array B. After in-place transposition these mnB = 12 vectors of C are stored in RM format in array B. This means the original mNB = 12 vectors now occupy array B in the permuted order  $\mathcal{M} = 0, 4, 8, 1, 5, 9, 2, 6, 10, 3, 7, 11$ .  $\mathcal{M}$  is the list form of the permutation vector transpose mapping of CMO C to RMO C or CMO  $C^T$ . Also,  $C^T$  is **identical to** m = 4 RB's of size MB by NB concatenated together.

For array A holding matrix A we do n parallel  $B \to B^T$  operations for each of the n concatenated subarrays B that make up the array A. After completion of these n parallel computation steps we have transformed CM matrix A in array A in-place to become the same matrix A but now A is represented in RB format in array A. Thus, after vector in-place transpose we have "cache blocked" matrix A! In conclusion, we hope the reader now clearly sees at a deeper level why NDS significantly improves MC DLA algorithm performance. The transformation of A in standard format to RB format by in-place vector transposition was orders of magnitude faster than ordinary scalar in-place methods.

## 4 A Comparison of GKK and TT Transpose Algorithms

Both these algorithms are claimed to be in-place. TT uses  $\min(m, n)$  extra storage and has an operation count that is  $\leq 24mn$  swaps plus O(mn) index operations. GKK uses a compact representation of the number of cycles, NC used by the transposition or permutation mapping  $\mathcal{M}$  of CMO A to RMO A. Its operations count is mn + NC moves plus the same number of index computations Also, there is the apriori computation of the cycle structure of  $\mathcal{M}$ . The GKK algorithm has good parallel implementations and is organized to use vector and cache blocking type operations as much as possible. Except for [13] there has been no implementation of the TT algorithm. The paper [20] does not mention parallelism. It does mention operations on "contiguous entries that could decrease cache misses" on page 380. Also, on the bottom of page 383 and the top of page 384 there is explicit mention of moving contiguous entries of A. Otherwise, there is no further mention of contiguous and or cache considerations.

#### 4.1 Storage Amounts for GKK and TT Algorithms

The TT algorithm requires  $\min(m, n)$  storage locations. The GKK algorithm generates a compact representation of the cycle structure of  $\mathcal{M}$ . Figure 2 of [10] studied random matrices whose sizes m, n were between 2 and 100. 45% of these matrices had less than 9 cycles in their  $\mathcal{M}$ . This was a surprising result for us. However, the storage cost to represent the cycle structure of any  $\mathcal{M}$  was very tiny. In Sect. 5 of [10] square matrices were considered and a order 19 example was discussed as having 190 cycles! Not mentioned was the storage cost of this structure which was a sparse matrix type row pointer and column index structure to represent these 190 cycles. Only 4 row pointers and 12 column indices were needed. This compares favorably with the TT amount or 19 locations. The TT papers discusses matrices with  $n = m^q$  whose size is  $|A| = m^{q+1}$ . These matrices have a maximum cycle length of size q + 1. They represent a generalization of square matrices where q = 1. Such matrices represent a set worst cases for GKK type algorithms. To give some idea what GKK does for this case we let m = 10and choose q = 1, 2, 3, 4, 5. The GKK algorithm found the number of cycles to be 55, 340, 2530, 20008, 166870. However, the cycle representation storage for these five matrices is 15, 46, 65, 289, 93. These latter values compare favorably with the constant TT value of m = 10.

#### 4.2 Vector Transpose and $n \times m$ A Matrices Where $n = km^q$

Both the TT and vector transpose, see Sect. 3, algorithms consider matrices A where  $n = km^q$ . For TT, k < m. For vector transpose, k > 1 is arbitrary so q can be one. In Sect. 3 these types of matrices give good performance. A user can set the LDA of A so this condition always holds; see Sect. 1.2 of [10]. In Sect. 3 of [10] we discuss the case where m and n are not multiples of blocking factors  $m_b$  and  $n_b$ . The TT authors handle this related issue by using their Lemmas 3 and 4. We close this section by noting that the cycle structure of A can vary greatly when k > 1 versus k = 1 in the TT algorithm; we give two examples where k = 1, 2: q = 2, m = 3 and q = 1, m = 29. In the first example, we get 8 cycles of length 3 and 3 singleton cycles versus 1 cycle of length 52 and 29 singleton cycles; in the second example, we get 406 cycles of length 3 and 29 singleton cycles versus single cycles of length 1640 and 40 and 2 singleton cycles.

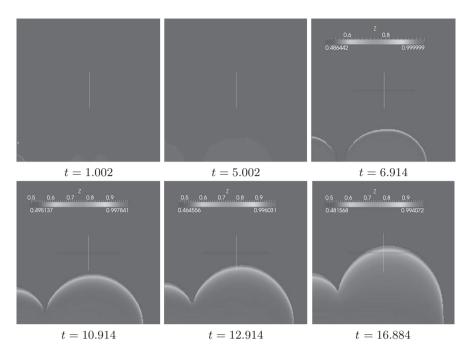

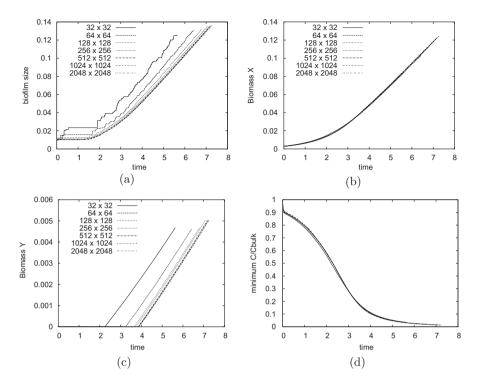

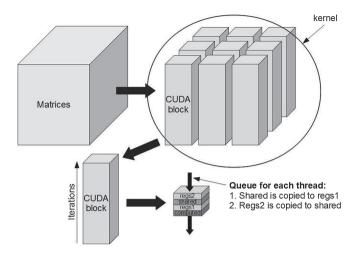

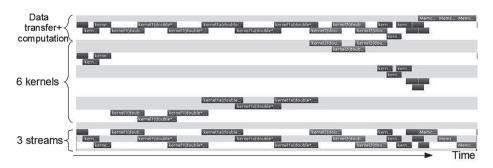

#### 4.3 A Clarifying Example with n = 673 and m = 384